-

如何利用FPGA進行時序分析設計

FPGA即現場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

2017-06-23

FPGA 時序分析

-

高性能射頻調制器促成多載波通信發送器設計

蜂窩發送器的設計依賴于能夠保持高線性度和高動態范圍的高性能RF調制器。隨著多載波發送器的增長,RF調制器必須保持低噪聲基底,從而提供較高的性能指標,通常取決于二階或三階互調。本文討論了這些需求,并說明MAX2022能夠滿足典型四載波WCDMA發送架構的要求。

2017-06-23

高性能 射頻調制器 多載波 發送器

-

被動元件持續缺貨 原因何在?

被動元件最大漲價潮來襲。市場傳出,龍頭廠國巨再度向客戶端發出最新供貨和價格資訊,第3季將有特殊品項的積層陶瓷電容(MLCC)交貨期拉長至六個月,價格將調漲15%至30%,為近17年最大的調漲幅度。若國巨這次能夠漲價成功,將是被動元件業自2000年最高峰以來最大漲幅。

2017-06-23

被動元件 MLCC 缺貨 漲價

-

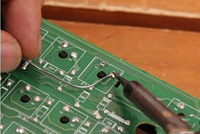

快速檢測出PCB板故障問題的方法

制作PCB板并非簡單的按流程來做完板子,鉆個孔打上元器件就好了。PCB的制作并不難,難的在于制作完成后的故障排查。無論是個人愛好者還是行業工程師,對于PCB電路板在調試的時候遇到問題也是相當的頭疼,就好比程序員遇到BUG一樣。

2017-06-22

PCB板 故障排查

-

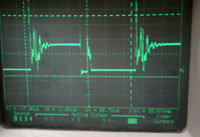

干擾波形是來自探頭接地還是通道串擾?

很多工程師在使用示波器測量開關電源輸出信號時,會發現兩個測量通道之間存在互相干擾的情況。這個干擾是否來自于通道之間呢?我們實測來驗證一下。

2017-06-22

干擾波形 示波器 測量測試

-

數字接收機中高性能ADC和射頻器件的動態性能要求

基站系統(BTS)需要在符合各種不同標準的同時滿足信號鏈路的指標要求。本文介紹了一些信號鏈路器件,例如:高動態性能ADC,可變增益放大器,混頻器和本振,詳細介紹了它們在典型的基站中的使用,能夠滿足基站系統對高動態性能、高截點性能和低噪聲的要求。

2017-06-22

數字接收機 高速ADC 射頻器件 動態性能

-

超低抖動時鐘合成器的設計挑戰

該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。對于1GHz模擬輸出頻率,所產生的抖動信噪比SNR為:-20 × log(2 × π × f × tj) = -64dB。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預期。關于元器件變量和折衷方案的討論為進一...

2017-06-22

低抖動 時鐘合成器 設計方案

- 噪聲中提取真值!瑞盟科技推出MSA2240電流檢測芯片賦能多元高端測量場景

- 10MHz高頻運行!氮矽科技發布集成驅動GaN芯片,助力電源能效再攀新高

- 失真度僅0.002%!力芯微推出超低內阻、超低失真4PST模擬開關

- 一“芯”雙電!圣邦微電子發布雙輸出電源芯片,簡化AFE與音頻設計

- 一機適配萬端:金升陽推出1200W可編程電源,賦能高端裝備制造

- 進迭時空發布 K3 芯片 以 RISC-V 架構賦能智能計算新場景

- 意法半導體公布2025年第四季度及全年財報

- 納米級精度加持:3D白光干涉儀助力TGV束腰孔徑精準檢測

- Marki ADM-10703PSM 寬帶低噪聲放大器(LNA)核心介紹

- 對標EN ISO 15118-20:2022 歐盟準入級智能交流充電樁技術方案

- 車規與基于V2X的車輛協同主動避撞技術展望

- 數字隔離助力新能源汽車安全隔離的新挑戰

- 汽車模塊拋負載的解決方案

- 車用連接器的安全創新應用

- Melexis Actuators Business Unit

- Position / Current Sensors - Triaxis Hall