【導(dǎo)讀】當(dāng)數(shù)據(jù)處理需求從云端向網(wǎng)絡(luò)邊緣加速遷移,傳統(tǒng)處理器在實(shí)時(shí)性、靈活性與能效能效方面的局限日益凸顯。在這一變革中,現(xiàn)場可編程門陣列(FPGA) 正以其獨(dú)特的硬件可重構(gòu)性和并行處理能力,成為解鎖下一代邊緣智能的關(guān)鍵。它不僅僅是計(jì)算的執(zhí)行者,更是連接傳感器、機(jī)器與算法的敏捷“橋梁”,能夠?yàn)樽灾鳈C(jī)器人、高端醫(yī)療影像等對時(shí)延與精度有極致要求的應(yīng)用,提供從高速接口到實(shí)時(shí)推理的端到端硬件加速解決方案。

當(dāng)數(shù)據(jù)處理需求從云端向網(wǎng)絡(luò)邊緣加速遷移,傳統(tǒng)處理器在實(shí)時(shí)性、靈活性與能效能效方面的局限日益凸顯。在這一變革中,現(xiàn)場可編程門陣列(FPGA) 正以其獨(dú)特的硬件可重構(gòu)性和并行處理能力,成為解鎖下一代邊緣智能的關(guān)鍵。它不僅僅是計(jì)算的執(zhí)行者,更是連接傳感器、機(jī)器與算法的敏捷“橋梁”,能夠?yàn)樽灾鳈C(jī)器人、高端醫(yī)療影像等對時(shí)延與精度有極致要求的應(yīng)用,提供從高速接口到實(shí)時(shí)推理的端到端硬件加速解決方案。

這些優(yōu)勢對于優(yōu)化生產(chǎn)質(zhì)量和效率尤為重要,在高風(fēng)險(xiǎn)的關(guān)鍵基礎(chǔ)設(shè)施中更是如此,在這些環(huán)境中,實(shí)時(shí)監(jiān)控、快速決策和可擴(kuò)展能力可能決定成敗。然而,打造滿足這些需求的設(shè)備絕非易事。

這正是萊迪思的邊緣人工智能傳感器橋接解決方案發(fā)揮作用的地方。該解決方案專為簡化邊緣系統(tǒng)的開發(fā)和部署而設(shè)計(jì),結(jié)合了萊迪思現(xiàn)場可編程門陣列(FPGA)和英偉達(dá)(NVIDIA)Holoscan技術(shù)的優(yōu)勢,為下一代智能邊緣計(jì)算能力提供低延遲、高吞吐量的連接能力。

邊緣連接面臨的挑戰(zhàn)

邊緣開發(fā)者不得不在條件極為受限的環(huán)境中工作。由于可用的物理空間、電力和計(jì)算能力有限,邊緣并非總是適合高性能處理能力的理想環(huán)境,更不用說完全自動化的系統(tǒng)了。

對于開發(fā)者而言,這是一個(gè)長期存在的問題。即使如今的半導(dǎo)體采用先進(jìn)的處理節(jié)點(diǎn)制造,大大提高了計(jì)算能力,但它們?nèi)允芸臻g和連接限制。這些先進(jìn)節(jié)點(diǎn)的加入限制了芯片的輸入/輸出(I/O)能力,使系統(tǒng)設(shè)計(jì)變得更為復(fù)雜,尤其是當(dāng)這些設(shè)備需要集成各種傳感器和設(shè)備輸入時(shí)。

此外,在當(dāng)今這個(gè)時(shí)代,系統(tǒng)需求遠(yuǎn)非一成不變。隨著人工智能(AI)和機(jī)器學(xué)習(xí)(ML)模型等解決方案不斷演進(jìn),它們所需的資源在不斷變化,需要獲得這些資源的速度也越來越快。計(jì)算需求持續(xù)上升,而電池和熱限制條件基本保持不變,這為開發(fā)者制造了一個(gè)困難且互相矛盾的場景。

FPGA聯(lián)合英偉達(dá)Holoscan的解決方案

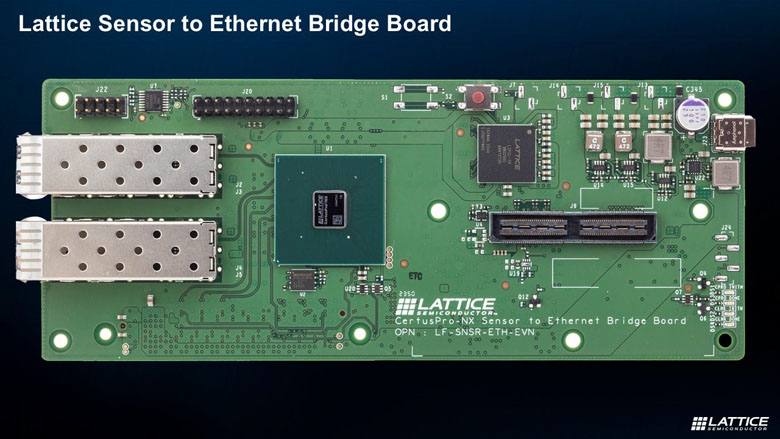

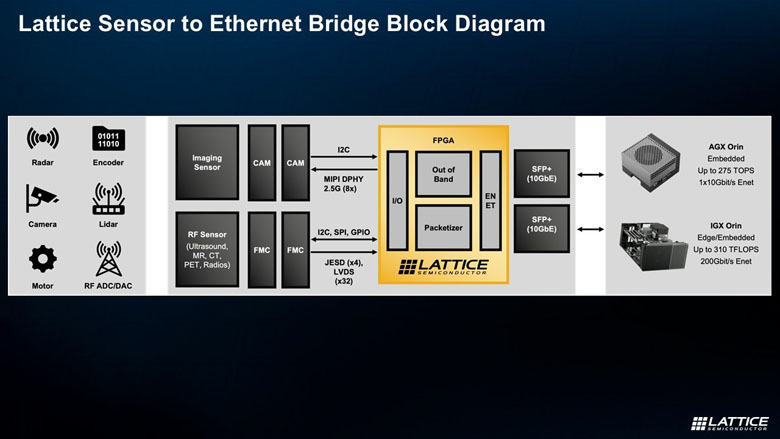

為了克服這些限制,開發(fā)者需要一種將靈活性與高性能連接能力相結(jié)合的解決方案。通過結(jié)合萊迪思FPGA和NVIDIA Holoscan軟件的力量,開發(fā)者可以創(chuàng)建一個(gè)支持快速開發(fā)互連的邊緣應(yīng)用的基礎(chǔ)平臺。聯(lián)合開發(fā)的傳感器到以太網(wǎng)橋接板設(shè)計(jì)將通用Lattice CertusPro?-NX FPGA的可編程性與Holoscan的處理能力相結(jié)合,以在邊緣應(yīng)用中支持無縫的傳感器融合。

該解決方案的主要優(yōu)勢包括:

低延遲、高吞吐量且可擴(kuò)展的傳感器數(shù)據(jù)流傳輸。

全棧解決方案,能將傳感器數(shù)據(jù)直接傳輸至英偉達(dá)(Nvidia)的本地存儲。

即用型開源軟件。

內(nèi)部AXI數(shù)據(jù)流和APB控制總線支持模塊化、可配置的傳感器配置和數(shù)據(jù)流傳輸。

支持多達(dá)2條10G以太網(wǎng)通道。

該解決方案的優(yōu)勢和實(shí)用性源于其基于FPGA的架構(gòu)。FPGA作為NVIDIA IGX Thor和AGX Orin硬件組件之間的智能橋梁,能夠?yàn)橹醒胗?jì)算單元分擔(dān)大量處理任務(wù)。萊迪思FPGA尤其適合這一角色,因?yàn)槠渚邆涞凸奶匦浴⒋_定的并行處理能力、I/O可擴(kuò)展性以及內(nèi)置的安全特性。這使得它們能夠高效地預(yù)處理傳感器數(shù)據(jù),同時(shí)降低整體系統(tǒng)功耗和延遲,并為中央計(jì)算單元騰出計(jì)算資源,以運(yùn)行更復(fù)雜的人工智能(AI)模型。

精簡邊緣運(yùn)算帶來的影響

這些強(qiáng)大的技術(shù)協(xié)同作用,有助于在各種場景中簡化并加速智能邊緣系統(tǒng)的部署,同時(shí)解決邊緣人工智能(AI)開發(fā)者面臨的最緊迫挑戰(zhàn)。

為平衡日益增長的算力需求與強(qiáng)大的輸入/輸出(I/O)支持能力,這款基于FPGA的解決方案將所有傳感器和輸入數(shù)據(jù)打包,并通過以太網(wǎng)進(jìn)行數(shù)據(jù)流傳輸。這種方法利用了以太網(wǎng)的普適性以及其在成本效益和高帶寬方面的優(yōu)勢,能夠在不占用過多空間的情況下實(shí)現(xiàn)高效的數(shù)據(jù)傳輸。采用這種設(shè)計(jì),F(xiàn)PGA能夠支持將傳統(tǒng)I/O功能與新需求進(jìn)行橋接,對所有數(shù)據(jù)進(jìn)行聚合和打包,簡化從傳感器到處理器的數(shù)據(jù)傳輸過程。

該解決方案還支持為滿足不斷演變的系統(tǒng)需求而進(jìn)行的必要更新。為滿足不斷變化的系統(tǒng)需求,F(xiàn)PGA支持低功耗計(jì)算機(jī)視覺和AI處理,能夠降低鏈路帶寬和功耗,同時(shí)為中央計(jì)算單元分擔(dān)這些任務(wù)。隨著系統(tǒng)發(fā)生變化以及新任務(wù)和工作負(fù)載的引入,可根據(jù)需要重新編程FPGA,以保持最高效地平衡分配處理任務(wù)。

構(gòu)建更智能、更快速且更具可擴(kuò)展性的邊緣系統(tǒng)

隨著邊緣解決方案持續(xù)推動各行各業(yè)變革,在數(shù)據(jù)源頭高效且安全地聚合和處理傳感器數(shù)據(jù)變得至關(guān)重要。通過將萊迪思FPGA的強(qiáng)適應(yīng)性與英偉達(dá)NVIDIA Holoscan功能相結(jié)合的傳感器橋接解決方案,使得開發(fā)者能夠克服常見限制,加速邊緣部署的成功實(shí)現(xiàn)。

推薦閱讀:

集中供電,分布智能:面向區(qū)控架構(gòu)的汽車配電解決方案全景掃描

深入恩智浦MCX系列,解鎖邊緣AI與高能效計(jì)算的融合設(shè)計(jì)

AAA電池怎么選?5款A(yù)AA堿性電池實(shí)測,結(jié)果可能出乎意料