【導讀】在芯片技術飛速發展的當下,芯片設計呈現出規模急劇擴張、復雜度不斷攀升的態勢。特別是針對人工智能(AI)和高性能計算(HPC)這類對算力要求極高的負載場景,把所有功能一股腦兒集成在單一平面裸片上,已然成為一項極具挑戰甚至難以實現的任務。然而,要精準判斷何時該切換到多裸片(Die)封裝方案,卻并非能輕松做出的決定。

在芯片技術飛速發展的當下,芯片設計呈現出規模急劇擴張、復雜度不斷攀升的態勢。特別是針對人工智能(AI)和高性能計算(HPC)這類對算力要求極高的負載場景,把所有功能一股腦兒集成在單一平面裸片上,已然成為一項極具挑戰甚至難以實現的任務。然而,要精準判斷何時該切換到多裸片(Die)封裝方案,卻并非能輕松做出的決定。

多裸片技術的優勢已有詳實的行業論證。該技術允許設計人員將不同功能拆分至獨立裸片,有助于提升生產良率;同時可針對部分功能模塊采用成熟且低成本的工藝節點,在降低成本的同時提高產品可靠性。隨著相關技術標準的普及和設計工具的迭代優化,多裸片方案的落地難度已有所降低。此外,面對日益增長的性能需求,以及先進工藝節點流片一次成功率下降的行業現狀,企業為保持競爭力、更高效地平衡功耗、成本與可靠性,紛紛開始采用多裸片技術方案。

推動多裸片封裝發展的兩大核心驅動力,源自芯片設計到制造流程的兩端。“第一大驅動力是功能解耦,”西門子EDA(Siemens EDA)中央工程解決方案總監Pratyush Kamal表示,“裸片的尺寸正變得越來越大,尤其是在先進工藝節點中,其面積已逼近光刻機的掩膜版尺寸極限——而晶圓制造工藝恰恰受限于掩膜版的規格。我們正致力于研究Cerebras公司如何通過創新技術實現跨掩膜版邊界的芯片設計。目前,行業內也在借助晶圓級封裝技術達成類似目標,具體包括采用背面重布線層(RDL)等工藝。但對于單片集成設計而言,掩膜版尺寸始終是一道難以突破的瓶頸。第二大驅動力則是系統集成。這其中涉及嵌入式穩壓器的應用,我們正將更多元器件集成到封裝內部。從根本上來說,縮小電子設計的占位面積,就能有效降低功耗、提升性能。正是這兩大因素,共同推動了先進封裝技術的落地應用。”

然而,在種類繁多的多裸片技術路線中,哪一種方案最優,始終是一個沒有標準答案的難題。“設計人員可以選擇采用通用封裝方案,通過UCIe或其他裸片間互聯技術,實現兩顆裸片的并排集成;也可以選擇成本更高的先進封裝方案,在裸片之間嵌入硅中介層;甚至還能采用2.5D/3D堆疊技術,實現裸片的垂直堆疊。不同技術路線的適用門檻存在差異。”楷登電子(Cadence)產品營銷總監Mayank Bhatnagar解釋道,“從性能角度來看,如果一款芯片的所有功能能夠在最先進的工藝節點上實現單片集成,那么它無疑能達到最優性能。但這一結論的成立需要滿足諸多前提條件,而這些條件在多數實際場景中往往難以全部達成。這也是為什么高性能計算芯片會率先采用先進封裝技術的原因。理論上,單片集成設計的性能表現十分可觀,但面對當前的AI與HPC負載,能否實現單片集成本身就是一個巨大的未知數。即便可以實現單片集成,過大的裸片面積也會導致良率大幅下降。因此,企業選擇多裸片方案的考量標準,有時并非某一設計的性能表現,而是能否以經濟可行的方式實現足夠大的芯片規模。”

在多數場景下,促使設計人員選擇功能解耦的核心動因,是需要在超過單一裸片面積的空間內集成更多計算資源,但這一決策還需綜合考量其他因素。“設計人員可能希望復用芯粒(Chiplet)中的部分知識產權(IP)核,因為這部分設計的功能通常較為穩定,無需頻繁迭代。”新思科技(Synopsys)產品管理高級總監Amlendu Shekhar Choubey表示,“此外,設計人員還可能需要采用異構集成技術,針對不同功能模塊匹配最適合的工藝節點。這些因素都會在決策過程中起到關鍵作用。我們提供的設計流程,能夠讓系統架構師在完成寄存器傳輸級(RTL)代碼或網表設計之前,就對這些因素進行權衡并做出決策。一旦明確了系統的功能需求與設計概念,架構師便可借助我們的工具流程,結合目標技術方案的相關信息開展前期設計探索。例如,基于初步的功能劃分,判斷多裸片架構是否適用;若適用,應如何進行架構設計與功能拆分,需要權衡哪些因素;是選擇垂直堆疊、水平集成,還是針對不同裸片采用混合集成方案。在啟動RTL代碼或網表設計之前,就能對功耗、性能與面積(PPA)的各項指標進行全面評估,這為架構師提供了強有力的支撐,助力其在前端設計啟動前做出最優決策。”

在這一階段,設計團隊需要敲定多項頂層設計決策。“項目啟動前,我們會以功耗、性能與面積(PPA)指標為核心,制定架構層面的技術規格,這也是多裸片方案決策的關鍵階段,”新思科技硬件工程經理Esha Dubey表示,“隨后,團隊還需評估成本、功耗以及所需的熱仿真方案——這些均是芯片架構師需要決策的內容。若采用2D、2.5D或多裸片3D堆疊設計,則需要先完成相應的布局規劃。接下來,需開展裸片間互聯的合規性檢查;同時,由于我們也提供各類IP核,設計團隊還需確定IP核之間的互聯方案。”

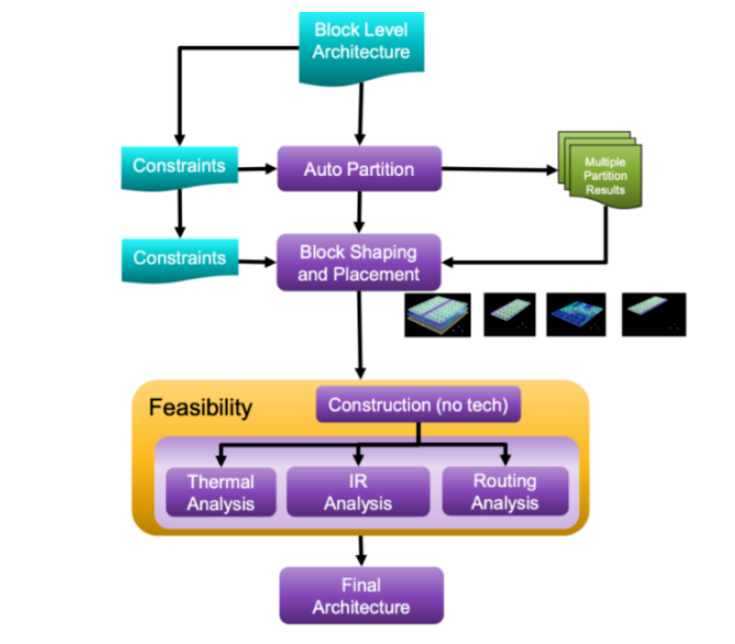

圖1 多裸片架構設計流程

圖表:模塊級架構設計流程,包含自動劃分、形狀優化、可行性分析及最終架構確定等環節。來源:新思科技(Synopsys)

從單片集成轉向多裸片方案的決策,取決于從架構設計到制造成本的諸多因素。這一轉型兼具技術屬性與戰略屬性,會對芯片的設計和制造全流程產生影響。為深入理解這一轉型趨勢,有必要探究這些因素之間的相互作用,以及它們對芯片產業發展方向的影響。

“我們需要先了解芯粒生態系統的形成邏輯。”是德科技EDA(Keysight EDA)EDA產品集成經理Stephen Slater表示,“過去,單一裸片的尺寸不斷增大,在晶圓上占據的面積越來越多,這導致了一系列制造問題,例如晶圓上出現局部區域參數超標。一旦出現此類問題,整個裸片都將報廢,最終導致良率極低。通過將芯片功能拆分為更小的模塊,單枚晶圓可產出的裸片數量會顯著增加,從而有效提升生產良率。FPGA廠商、CPU廠商以及NVIDIA等行業領軍企業,率先通過多芯片互聯技術實現了計算功能的擴展,達成了單一晶圓工藝升級無法企及的性能目標。隨著越來越多的復雜功能被轉移至封裝環節,業界開始更加關注如何規避潛在的性能瓶頸。例如,在實現芯片間高速信號傳輸時,信號互聯會不可避免地帶來一定的延遲,同時存在串擾風險。目前,芯粒生態系統中的多數企業都會采用UCIe等數字標準來實現高速互聯。UCIe標準同時支持通用封裝和先進封裝:在通用封裝方案中,通常采用傳統的有機封裝基板,信號通過基板實現芯片間傳輸;而在先進封裝方案中,則會引入硅基互聯結構——這種硅基互聯本身就是一枚集成電路,需要與互聯的芯粒進行協同封裝。后者作為一種高密度互聯方案,能夠支持超高數據傳輸速率,同時實現最大化的互聯密度。”

這就要求工程團隊投入更多精力開展信號完整性(SI)和電源完整性(PI)分析。“這是我們重點關注的領域,我們發現客戶正投入大量研發周期用于這類互聯鏈路的設計與優化,”Slater補充道,“設計人員需要特別關注版圖布局,尤其是硅中介層的布局——由于中介層沒有用于回流電流的實心接地平面(通常采用網格狀接地平面),其布局設計的難度更高。此外,芯粒系統中一個日益凸顯的問題是:如何通過低阻抗、低電阻的路徑,為芯片各模塊精準供電。我們還發現,采用先進封裝技術的應用場景,往往是大電流、低電壓的工作場景,這為電源垂直傳輸設計帶來了巨大挑戰。”

多裸片封裝方案需要投入更多的研發工作量和時間成本,且根據技術路線和目標負載的不同,其初期實施成本可能會顯著高于單片集成方案。“只有在‘非用不可’的情況下,企業才會選擇多裸片方案,”Bhatnagar指出,“多裸片設計意味著需要多次流片,因此掩膜版和封裝的整體成本會大幅上升。”

多裸片方案的成本控制,在一定程度上取決于工程團隊對該類架構的技術駕馭能力。“綜合考量性能、功耗、面積和成本等因素,若芯片功能可實現單片集成,其性能無疑是最優的,”Bhatnagar表示,“一旦采用裸片間互聯,就必然會產生性能瓶頸,因為數據傳輸需要經過互聯鏈路——這也是功能劃分至關重要的原因。設計人員需要通過合理的功能劃分,將裸片間的數據傳輸量降至最低。”

多裸片設計中的功耗問題同樣備受關注。“裸片間的數據傳輸會產生額外的功耗開銷,但另一方面,如果部分功能模塊可以沿用成熟工藝節點,而非采用漏電率更高的先進工藝,就能實現功耗的節約,”Bhatnagar解釋道,“當芯片被拆分為多裸片后,原本芯片內部的標準單元互聯,就轉變為通過封裝實現的裸片間互聯。因此,單次大規模數據傳輸的功耗,會遠高于單片集成芯片內部的數據傳輸功耗。這是所有客戶都希望大幅改善的痛點;而作為UCIe和裸片間互聯IP核供應商,降低互聯功耗也是我們的首要目標——因為客戶在決定采用多裸片方案的那一刻,就會直面這一問題。”

多裸片封裝的經濟性考量

從平面系統級芯片(SoC)轉向多裸片封裝的決策,經濟性是核心考量因素之一。

“如果將整個SoC芯片遷移至2nm等先進工藝節點,晶圓成本——即單片裸片的成本會非常高昂。此外,若芯片設計規模較大,良率會偏低。高晶圓成本疊加低良率,最終會導致單顆芯片的成本居高不下,”Bhatnagar解釋道,“以GPU或高性能計算核心的遷移為例,采用多裸片方案后,設計人員只需將這部分核心模塊遷移至先進工藝節點,其余功能模塊則可繼續沿用成熟工藝。這種情況下,不僅晶圓成本和單顆芯片成本會降低,設計成本也能得到有效控制。例如,射頻(RF)接口模塊從多裸片方案中獲益有限,設計人員完全可以保留其成熟工藝方案——這部分模塊經過充分驗證,性能穩定可靠,不僅能降低設計成本,還能提升產品的整體可靠性,無需將所有模擬電路模塊重新設計并遷移至新工藝節點。”

過去幾年間,封裝成本也在持續下降。隨著新廠商入局,先進封裝技術的可及性顯著提升,設計人員也在積極利用這一利好條件。

多裸片方案的關鍵考量因素

芯片架構師通常是決定是否采用功能解耦方案的核心角色。他們會根據產品需求定義芯片功能,例如,超大規模數據中心可能會要求芯片支持112、224或448 Gbps的傳輸吞吐量。

“基于這些需求,架構師會從IP核產品組合中篩選合適的方案,判斷其是否支持多裸片架構。”新思科技SoC工程高級總監Shawn Nikoukary表示,“接下來需要重點考量功耗指標——尤其是在數據中心應用中,功耗是最重要的設計約束條件之一。因此,在架構設計階段,團隊必須充分挖掘所有可能的功耗優化空間,而這往往會推動設計方案向先進封裝技術傾斜。為了在低功耗、小工藝節點下實現IP核的超高數據傳輸速率,采用先進封裝技術成為一種必然選擇。”

此外,還需考量架構設計和工具鏈的適配性。“多裸片方案的核心轉折點在于系統集成的復雜度,而非單純的工藝制程升級,”ChipAgents首席執行官William Wang表示,“當系統級集成的各項指標(延遲、帶寬、電源域、復位機制、時鐘同步)無法通過單片集成的RTL設計和后期物理簽核進行可靠驗證時,先進封裝技術就成為必然選擇。芯粒的邊界,將架構設計的假設條件轉化為硬性的技術約束。一旦邏輯功能跨裸片分布,接口的正確性、延遲特性、協議規范以及電源和復位的響應行為,都必須被明確定義并持續驗證。這類隱性的設計違規,是導致芯片后期驗證失敗的主要原因之一。”

設計工具鏈本身也需要具備足夠的魯棒性。“工具鏈失效的根源,在于架構設計的意圖無法通過機器自動驗證。”William Wang指出,“技術規格文檔、設計示意圖、RTL代碼和集成腳本,都會隨著項目推進產生偏差。ChipAgents的核心優勢在于,能夠將架構設計意圖轉化為RTL設計和集成階段的可自動驗證約束條件,并在封裝方案和芯片流片決策敲定前完成驗證。”

多裸片設計面臨著諸多相互交織的挑戰。盡管技術不斷進步,但EDA工具的發展速度仍落后于封裝技術的迭代步伐。“設計過程中必須開展仿真驗證,而信號完整性是其中的關鍵環節。”Shawn Nikoukary表示,“過去的封裝仿真主要針對PCB封裝,如今則需要針對芯片內部的硅基結構進行仿真。相關的仿真類型和工具正在快速發展。多裸片方案的決策并非由單一因素決定,而是需要綜合考量IP核、架構設計、生態系統和工具鏈等多個維度,是一個復雜的系統性問題。如今的封裝廠商正處于行業的核心位置——他們需要整合各類芯粒,解決熱學、電學、電磁干擾與壓降(EMIR)、力學等多物理場的仿真驗證問題,同時還需與生態伙伴協作,確保設計方案所需的工藝設計套件(PDK)能夠及時到位。只有這樣,當芯片設計完成時,新技術才能實現量產落地,同時保證良率達標。”

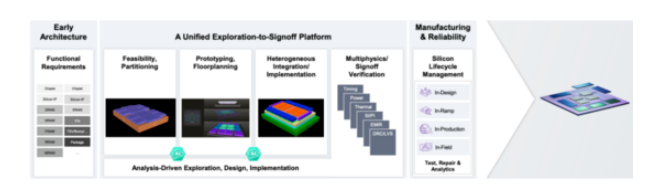

圖表:面向前期架構設計的一體化探索至簽核平臺,涵蓋功能需求分析、可行性驗證、原型設計及量產制造等環節。來源:新思科技(Synopsys)

不過,設計工具的性能也在持續提升。“與早期的先進封裝設計工具相比,如今的工具效率比手工布局高出10倍以上。”Shawn Nikoukary補充道,“工具鏈已全面引入人工智能技術實現自動化設計,相關技術仍在快速迭代。這并非是一個挑戰疊加另一個挑戰的困境,而是有越來越多的解決方案正在加速落地,行業也在不斷探索更高效的設計方法。例如,當一個封裝中需要集成50顆以上的芯粒時,傳統的設計流程和工具已經完全無法滿足需求。”

那么,企業為何要選擇多裸片方案?“其核心目標是在降低成本的同時提升性能。”西門子EDA的Pratyush Kamal表示,“高帶寬內存(HBM)就是一個典型案例——它屬于系統集成的范疇,而非功能解耦。過去,內存芯片通常位于主板上(如DDR內存),而現在,HBM已被集成到封裝內部。”

類似的技術趨勢也出現在6G通信領域。“各國政府都在大力推動三維異構集成(3DHI)技術的發展,這是因為6G通信需要使用100GHz以上的頻譜資源。”Pratyush Kamal解釋道,“通信原理的基本常識告訴我們,天線的尺寸與載波波長直接相關,天線的間距不能小于某一臨界值。因此,當6G載波的波長進入微米級別時,天線就必須集成到封裝內部,形成完整的6G通信棧。美國國防高級研究計劃局(DARPA)正致力于推動這一技術的研發,其他國家的政府也在積極跟進。這是由物理原理決定的技術發展方向。美國正在推進的‘下一代微電子制造計劃(NGMM)’就是一例——該項目由DARPA和得克薩斯州政府聯合資助,西門子是合作方之一。2024年,得克薩斯電子研究所獲得了15億美元的資金支持,用于建設三維異構集成制造設施。美國超過20家企業和高校都參與了該項目。實現6G技術的全面系統級應用,是我們的最終目標。”

未來展望

那么,如何才能降低工程團隊向多裸片方案遷移的門檻?業內的普遍共識是:減少技術路線的選擇冗余。

“對于希望參與開放式芯粒生態或芯粒交易市場的用戶而言,當前面臨的一大挑戰是技術方案的多樣性過于繁雜,”楷登電子的Bhatnagar表示,“目前,芯粒的技術變體數量過多。我負責UCIe和定制化Ultralink裸片間互聯IP核的相關工作,因此十分清楚技術變體的龐大規模。去年,我在為新入職員工做培訓時提到,僅在單一工藝節點下,不考慮3D堆疊方案,僅2D和2.5D集成方案就可以衍生出32種UCIe技術變體。這恰恰是問題的癥結所在——當市場被切割為過多細分領域時,企業很難開發出具有廣泛市場吸引力的芯粒產品。畢竟,企業可能針對A市場啟動芯粒研發,但兩年后產品面市時,市場需求或許已經轉向了C方向。因此,推動行業形成一定的技術共識與整合,將對多裸片技術的發展起到積極作用。”

推薦閱讀: