【導讀】三星電子傳來關鍵突破信號。據韓國媒體TheElec報道,其第七代高帶寬內存產品HBM4E已正式邁入基礎芯片后端設計階段,這一里程碑式進展標志著整體研發進程過半,量產時間表鎖定2027年。作為HBM模塊的“控制中樞”,基礎芯片的設計進程直接決定產品性能上限,而三星此次不僅劍指3.25 TB/s總帶寬、兩倍于HBM3E的能效等硬核指標,更以4納米工藝、雙軌研發策略構建競爭壁壘,為全球AI基礎設施的存儲效率革命注入新動能,也讓這場由三星、SK海力士、美光主導的技術競賽進入更關鍵的攻堅期。

據悉,HBM4E的基礎芯片目前已完成寄存器傳輸級(RTL)邏輯設計,正進行物理電路的布局與布線(即后端設計)。這一階段通常占芯片設計總周期的60%至70%,完成后將進入流片(tape-out)準備,由代工廠啟動試產。

作為HBM模塊的“控制中樞”,基礎芯片不僅負責管理數據讀寫速度,還承擔對上方堆疊DRAM的錯誤校正(ECC),直接決定整顆HBM的性能、穩定性與能效。

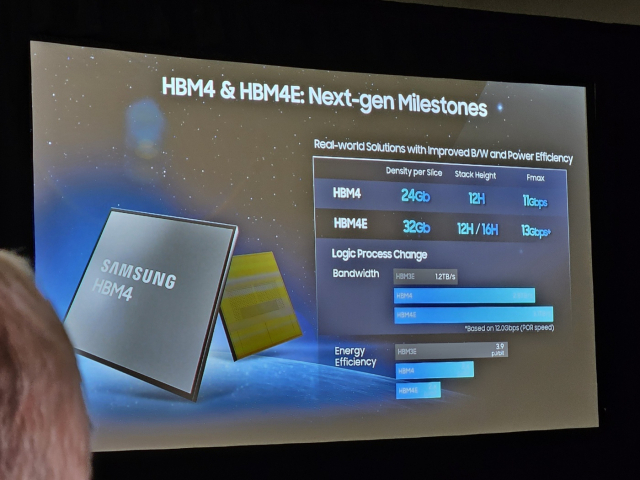

根據此前的信息,三星為HBM4E設定了技術指標:總帶寬目標高達3.25 TB/s,較當前主流的HBM3E提升約2.5倍;每針腳數據速率突破13 Gbps;同時維持2,048個I/O接口以確保兼容性。同時,其能效目標是HBM3E的兩倍以上。這對功耗敏感的數據中心和AI訓練集群至關重要。

為加速商業化進程,三星已向供應鏈發出明確信號:要求供應商在2026年3月前提交配套材料與設備供應計劃。公司內部更制定了覆蓋HBM4、HBM4E到HBM5(預計2029年推出)的完整路線圖,并同步運營兩個研發團隊——一個專注標準品,另一個專攻定制方案,形成“雙軌并行”策略。

TheElec稱,三星計劃在其自有的4納米FinFET工藝節點上制造HBM4E的基礎芯片,并由存儲器接口專家林大賢(Daihyun Lim)領銜I/O設計。林大賢曾任職IBM與GlobalFoundries,2023年加入三星,其經驗被視為攻克高速信號完整性難題的關鍵。

總結

三星HBM4E進入基礎芯片后端設計階段,既是其技術路線圖的關鍵跨越,也印證了全球HBM產業向高帶寬、優能效迭代的趨勢。依托4納米FinFET工藝、專家團隊攻堅及全鏈條布局,三星全力搶占AI存儲賽道。當前HBM市場短缺將持續至2028年,AI大模型需求激增背景下,HBM4E進展深刻影響全球AI服務器供應鏈格局。隨著2026年供應鏈配套落地及流片試產推進,三星能否憑此產品重塑競爭格局、為2027年量產及HBM5研發鋪路,備受行業關注,其技術突破也將助力AI基礎設施向高效低耗升級。